# Manufacture Testing of Digital Circuits

Prof. K-T Cheng

UC Santa Barbara

Prof. Srinivas Devadas

MIT

Prof. Kurt Keutzer

Mukul Prasad

University of California

Berkeley, CA

1

## **Class News**

Assignment of grade range for midterm on Wednesday Preliminary project report due 11/3

#### Second midterm

- Currently scheduled for 11/8 to be turned in 11/10!

- Reschedule 11/8 to be turned in 11/15

#### **Testing**

Apply a sequence of inputs to a circuit

Observe the output response and compare the response with a precomputed or "expected" response

Any discrepancy is said to constitute an error, the cause of which is a physical defect

- 1

#### **Defects and Fault models**

Manufacturing defects can manifest in a variety of ways:

- Bridging

- Contaminants

- Shorts

- Opens

- Transistors stuck-open

These need to be reduced to models:

- Single stuck-at-1, stuck-at-0

- Multiple stuck-at-1, stuck-at-0

- Delay fault models:

- Gate

- Path

- x {hazard-free, hazard-free robust}

#### Presently:

- single-stuck-at fault model ubiquitous

- some use of delay fault modeling

#### **Defect-related Yield Loss**

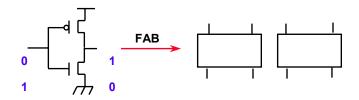

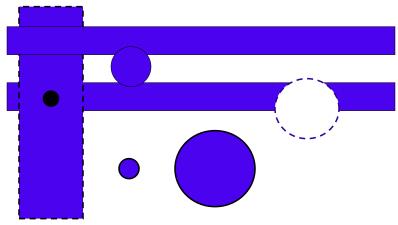

fatal defect types (two types of short circuits, one type of open)

.

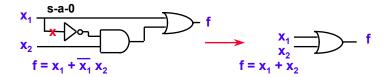

## **Defect Model: Stuck-At Faults**

Any input or internal wire in circuit can be stuck-at-1 or stuck-at-0

Single stuck-at-fault model: In the faulty circuit, a single line/wire is S-a-0 or S-a-1

Multiple stuck-at fault model: In the faulty circuit any subset of wires are S-a-0/S-a-1 (in any combination)

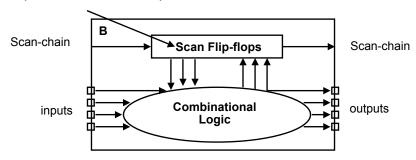

## **Reduce to Combinational Logic Problem**

add additional state to flip-flops (15 - 20% area overhead)

11

## **Test Generation**

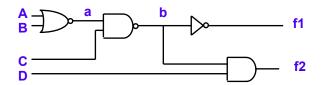

Choose a fault model, e.g., single stuck-at fault model

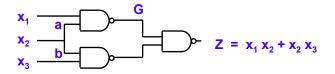

Given a combinational circuit which realizes the function  $f(x_1, x_2, \dots x_n)$ , a logical fault alters it to  $f_{\infty}(x_1, x_2, \dots x_n)$

Inputs detecting  $\infty$  are  $f \oplus f_{\infty}$  ( = 1 )

Interested in one vector

$$A = (a_1, a_2, \ldots, a_n) \in f \oplus f_{\infty}$$

## **Single Stuck-At Faults**

A fault is assumed to occur only on a single line.

This model is used because it has been found to be statistically correlated with defect-free circuits

13

#### **Activation and Path Sensitization**

In order for an input vector X to detect a fault a s-a-j, j = 0,1 the input X must cause the signal a in the normal (fault-free) circuit to take the value j.

The condition is necessary but not sufficient. Error signal must be propagated to output.

## **Fault Activation**

The faulty signal must be propagated along some path from its origin to an output

How to activate the fault?

15

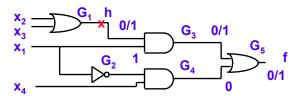

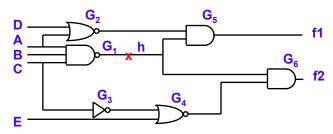

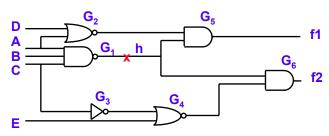

# **Fault Activation**

The faulty signal must be propagated along some path from its origin to an output

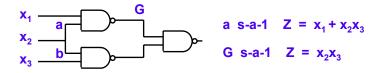

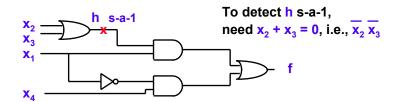

h s-a-1, for h to be 0, need  $x_2 = x_3 = 0$  ( $x_2 x_3$ )

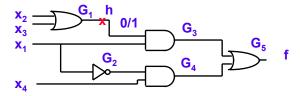

# **Fault Propagation**

The error signal must be propagated along some path from its origin to an output

h s-a-1, for h to be 0, need  $x_2 = x_3 = 0$   $(\overline{x_2} \ \overline{x_3})$ How to propagate the fault?

17

# **Fault Propagation**

The error signal must be propagated along some path from its origin to an output

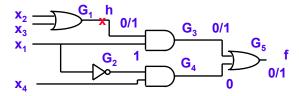

h s-a-1, for h to be 0, need  $x_2 = x_3 = 0$   $(\overline{x_2} \ \overline{x_3})$

Only one path G<sub>3</sub>, G<sub>5</sub>

In order to propagate an error through AND gate  $G_3$ , other input  $x_1 = 1$ . To propagate through  $G_5$ , need  $G_4 = 0$ ,  $x_1 + \overline{x_4}$

## **Single Path Sensitization (SPS)**

- 1. Activate: Specify inputs so as to generate the appropriate value (0 for s-a-1, 1 for s-a-0) at the site of the fault.

- 2.Propagate: Select <u>a</u> path from the site of the fault to an output and specify additional signal values to propagate the fault signal along this path to the output (error propagation).

- 3. Justify; Specify input values so as to produce the signal values specified in (2) (line justification).

19

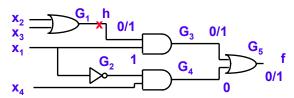

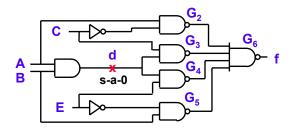

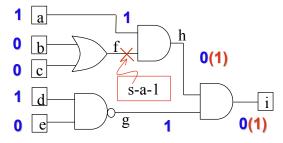

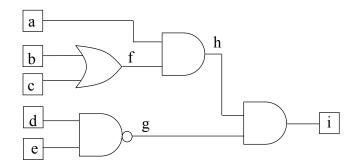

# **Sensitization Example - 1**

h s-a-1

Activate?

\_

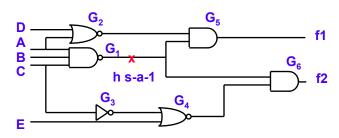

# **Sensitization Example - 2**

h s-a-1

Activate: To generate h = 0, need A = B = C = 1

Propagate?

\_

21

# **Sensitization Example - 2**

h s-a-1

To generate h = 0, need A = B = C = 1

Have a choice of propagating through  $G_5$  or via  $G_6$ . Propagating through  $G_5$  requires  $G_2 = 1$

$\Rightarrow$  A = D = 0 Contradiction

Propagating through  $G_6$  requires  $G_4 = 1 \implies C = 1$ , E = 0.

A valid test vector is ABCE

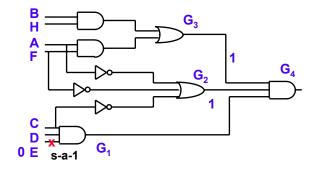

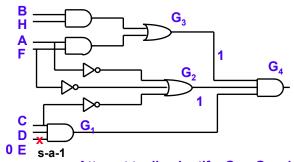

# **Line Justification**

$E s-a-1 \Rightarrow E = 0$

C = D = 1 to propagate through  $G_1$ .

To propagate through  $G_4$ , need  $G_2 = G_3 = 1$

How do we justify these values?

23

# **Line Justification - 2**

Attempt to <u>line justify</u>  $G_2 = G_3 = 1$

$G_3 = 1$  possible if A = F = 1 or B = H = 1

If A = C = 1, then  $G_2 = 0$ .

$$G_3 = 1 \Rightarrow B = H = 1$$

$G_2 = 1 \text{ needs } A = 0 \text{ or } F = 0$

Tests are !ABCD!EH, BCD!E!FH

# Redundancy

Existence of a fault does not change the functionality of a circuit ⇒ redundant fault

A test generation algorithm is deemed complete if it either finds a test for any fault or proves its redundancy, upon terminating.

25

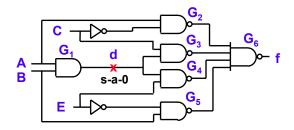

## **Completeness of SPS method?**

d s-a-0  $\Rightarrow$  A = B = 1 Propagate along G<sub>3</sub>, G<sub>6</sub>  $\Rightarrow$  C = 1 G<sub>2</sub> = G<sub>4</sub> = G<sub>5</sub> = 1 For G<sub>4</sub> = 1 either G<sub>1</sub> = 0 or E = 0 If G<sub>1</sub> = 0 fault is not activiated If E = 0 (B must be 1)  $\Rightarrow$  G<sub>5</sub> = 0 Inconsistency

# Completeness of SPS? - 2

Propagation along G<sub>4</sub>, G<sub>6</sub> also results in inconsistencies by symmetric argument

Is there no test?

27

## **Multiple Path Sensitization**

Error propagates down two paths  $\mathbf{G}_3$ ,  $\mathbf{G}_6$  and  $\mathbf{G}_4$ ,  $\mathbf{G}_6$  to output

It's natural to work backwards (justifying) and forwards (propagating) from point of fault activation but this focuses on sensitizing a single path

Attempting to sensitize a single path will not find a test for this fault

## First notation: D-Algebra/ D-calculus

Need to be able to deal with multiple "errors" at the inputs to a gate

D represents a signal which has value 1 in normal circuit, and value 0 in faulty circuit.

$$\bar{D} = 0/1$$

$$D = 0/1$$

$$D = 0$$

D, D behave like Boolean variables

29

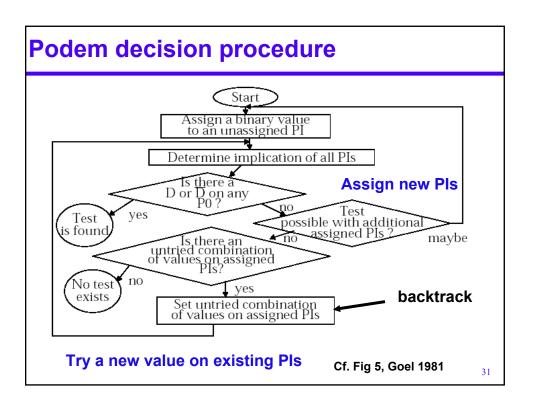

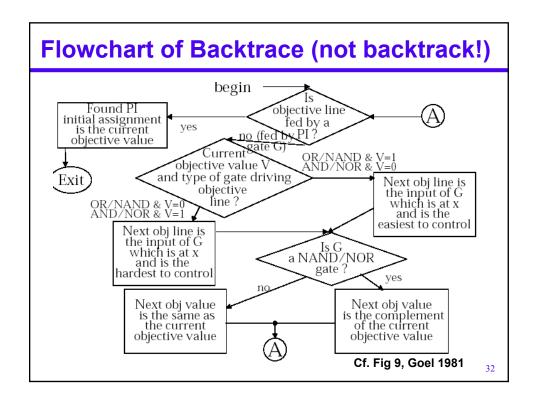

#### Podem strategy - Goel

Podem uses a brilliant simplification to avoid the single-path sensitization trap - only primary inputs are assigned a value

Values are assigned to primary inputs, then propagated forward – need a compatibility between required value and PI value

Continue to assign PI values one at a time

- Implicate values forward

- check to see if the faulty value has propagated to an output if so then you have a test

If at any point there is a conflict between the PIs and

- Exciting the faulty value

- Propagating the faulty value forward

backtrack – but only at the primary inputs, if you have tried all combinations then halt with failure to find test

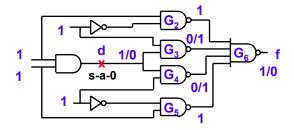

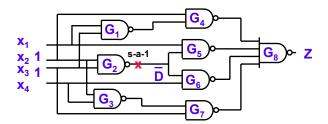

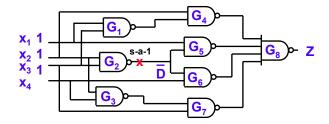

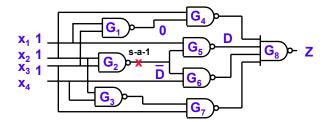

# **PODEM Example**

Initial objective: (0, G<sub>2</sub>)

Backtrace to PIs:  $x_2 = 1$

Objective:  $(0, G_2)$ Backtrace:  $x_3 = 1$ Implication:  $G_2 = \overline{D}$

33

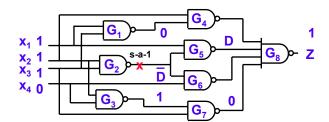

# Podem Example – 2a

D-frontier is {G<sub>5</sub>, G<sub>6</sub>}

Attempt to propagate through G<sub>5</sub>

Require  $x_1 = 1$

Implication?

# Podem Example – 2b

D-frontier is {G<sub>5</sub>, G<sub>6</sub>}

Attempt to propagate through G<sub>5</sub>

Require  $x_1 = 1$

Implication  $G_1 = 0$ ,  $G_4 = 1$ ,  $G_5 = D$

35

# Podem Example – 3a

Attempt to propagate D through G<sub>8</sub>.

Objective (1, G<sub>6</sub>)

Backtrace to set  $x_4 = 0$

Implication produces  $G_3 = 1$   $G_7 = 0$   $G_8 = 1$  failed in propagating error

# Podem Example – 3b

Attempt to propagate D through G<sub>8</sub>.

Objective (1, G<sub>6</sub>)

**Backtrace**

37

# Podem Example - 4

BACKTRACK to most recent assignment x<sub>4</sub>

Try alternative value  $x_4 = 1$

Implication results in  $G_3 = 0$ ,  $G_6 = D$ ,  $G_8 = D$

**Generated test 1111**

#### **Status on Podem**

Podem approach very successful

At the core of most ATPG systems today

**Spawned many additional innovations**

- FAN Fujiwara sophisticated backtrace

- Socrates Schulz learning

But if we had it all to do over ...

39

# **Another approach to ATPG**

The ATPG problem

The CIRCUIT-SAT problem

The Boolean Satisfiability (SAT) problem

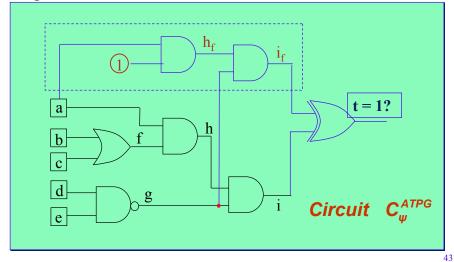

## The ATPG problem

#### Circuit C

- · A logic circuit

- A fault point

- A fault value

$$\psi = f, s - a - 1$$

Does there exist a value assignment to the primary inputs which distinguishes the faulted and correct circuits?

41

## The CIRCUIT-SAT problem

Does there exist a value assignment to the primary inputs which causes at least one primary output to assume logic value '1'?

#### ATPG as a CIRCUIT-SAT problem

Can we find an input value in which the faulty circuit and the good circuit differ?

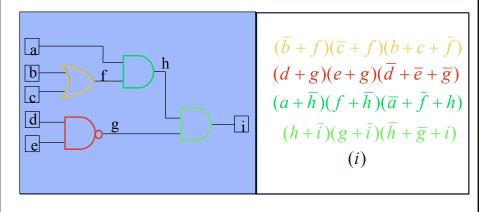

#### The Boolean Satisfiability (SAT) problem

#### Given a formula, f:

- ❖ Defined over a set of variables, V (a,b,c)

- **❖** Comprised of a conjunction of clauses (C₁, C₂, C₃)

- ❖ Each clause is a disjunction of literals of the variables V

Does there exist an assignment of Boolean values to the variables, V which sets at least one literal in each clause to '1'?

Example:

$$(a+b+c)(a+c)(a+b+c)$$

$$C_1 \qquad C_2 \qquad C_3$$

$a=b=c=1$

## **CIRCUIT-SAT** as a **SAT** problem

A set of clauses representing the functionality of each gate

A unit literal (i) clause asserting the output to be '1'

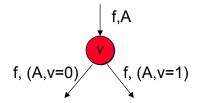

#### **Algorithm for SAT [DPLL-62]**

#### We have reduced ATPG to SAT- but then what?

Given: CNF formula  $f(v_1, v_2, ..., v_k)$ , and an ordering function Next\_Variable

```

Is_SAT(f, A)

{

if Check_SAT(f, A) return SAT

if Check_UNSAT(f,A) return UNSAT

v = Next_Variable(f, A)

if Is_SAT(f, (A,v=0)) return SAT

if Is_SAT(f, (A,v=1)) return SAT

return UNSAT

}

```

# **DPLL Algorithm – Unit Clause Rule**

- Unit Literal Propagation rule (Boolean

- . Constraint Propagation, BCP)

$$\begin{pmatrix} (a+b+c) \\ \parallel & \parallel \\ 0 & 0 \end{pmatrix} \qquad \mathbf{c} = \mathbf{1}$$

47

## **DPLL Algorithm - Pure Literal Rule**

• Pure-Literal rule: a

$$(a + ...) \qquad \boxed{(\overline{a} + ...)}$$

$$(a + ...) \qquad \boxed{(\overline{a} + ...)}$$

$$\vdots \qquad \vdots \qquad \vdots$$

$$(a + ...) \qquad \boxed{(\overline{a} + ...)}$$

$$\Rightarrow (\overline{a} + ...)$$

$$\Rightarrow (\overline{a} + ...)$$

ASSIGN  $a = 1$

$$SKIP a = 0$$

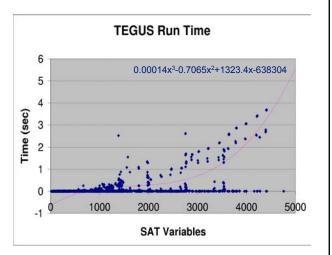

#### **Tegus Performance on Real Circuits**

#### Results:

- Of the 11,000 instances generated, 90% were solved in less than 1/100th of a second

- The remaining exhibited roughly a cubic growth in execution time

Why is ATPG Easy (although NP-Complete)?

40

#### **Current Status on Manufacture Test**

Practical approach to test: use scan – achieve 99%+ stuck-at coverage

Single stuck-at-fault testing for combinational logic is a ``solved problem''

- Despite the fact that it is NP-complete

- After 20+ years of research

- Results applied to combinational-equivalence checking

Single stuck-at-fault testing for sequential circuits is an intractable problem

- Despite the fact that it is also (only) NP-complete

- Even after 20+ years of research

- Time-frame expansion used in state-space search

Principal research focus is on ATPG for enhanced fault models

- Delay fault testing

Other approaches

- BIST

#### **PODEM**

```

PODEM(po, lvalue) {

jlist = po with logical value lvalue;

status = SEARCH_1(jlist);

return(status);

}

```

51

# SEARCH\_1(jlist)

```

SEARCH_1(jlist)

{

if (length of jlist is zero) return SUCCEED;

if (BACKTRACE(po, po_value, &pi, &pi_value) == FALSE)

return(FAILED);

if(IMPLY(pi, pi_value, jlist) != IMPLY_CONFLICT) {

search_status = SEARCH_1(JLIST);

if (search_status == FAILED) {

restore the state of the network to what it was

prior to the most recent primary input assignment;

search_status = SEARCH_2(jlist, pi, 1 - pi_value);

}

} else {

restore the state of the network;

search_status = SEARCH_2(jlist, pi, 1 - pi_value);

}

return(search_status);

}

```

# SEARCH\_2(jlist)

```

SEARCH_2(jlist, pi, pi_value)

{

backtracks = backtracks + 1;

if (backtracks > BACKTRACK_LIMIT) return(ABORTED);

if(IMPLY(pi, pi_value, jlist) != IMPLY_CONFLICT) {

search_status = SEARCH_1(jlist);

if (search_status == FAILED) {

restore the state of the network;

} else {

search_status = FAILED;

restore the state of the network;

}

return(search_status);

}

```